基本概念

图灵机

计算机的理论基础是——图灵机。

图灵机在理论上证明了:只要对数据进行处理、存储、传输三种简单的操作就能解决一切可计算的数学问题。

- 处理:按照有限规则对0,1的集合进行序列变换

图灵机的模型就是决定了计算机追求的就是一个字:快。(在规定的时间内完成对规律的表达)

冯诺依曼结构

结构基础

输出设备、输入设备、存储器、控制器、运算器

以运算器为中心。

在存储器中,指令和数据同样重要。

摩尔定律

物质基础

加快经常性事件

在计算机系统结构中加快的一个方式就是加快经常性事件。

要点:

- 辨认经常性事件

- 找出加快方法

CISC(复杂指令系统)

用硬件替代软件,用指令代替子程序。

但是容易使得硬件很冗余。

RISC(精简指令集)

找到频繁使用的代码。精简指令系统(不经常使用的就放弃掉),将多余的资源实现加快。可以把硬件部分增加寄存器的数量、做成多级的流水线等。

高速缓存Cache

利用局部性原理,将局部代码放在cache中,使得访存的速度与处理器的速度匹配。

Amdahl定律

计算机系统结构的总原则

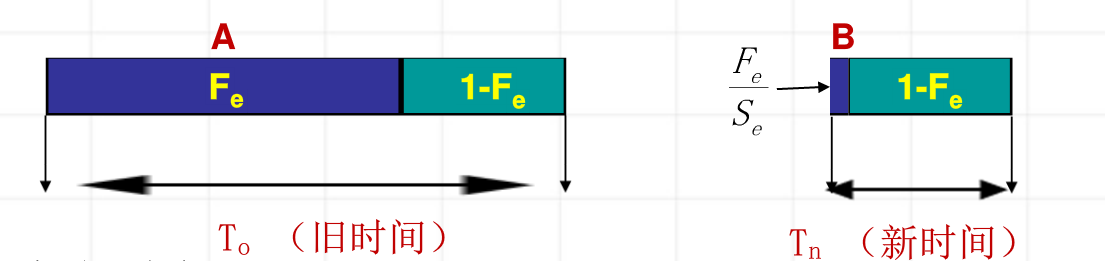

$$

加速比:S_n=\frac{新速度}{旧速度}=\frac{老时间}{新时间}=\frac{T_o}{T_n}\

S_n:系统加速比\

T_o:原执行时间\

T_n:新执行时间\

$$

$$

基本的Amdal定律:S_n=\frac{1}{(1-F_e)+\frac{F_e}{S_e}}\

S_e:被改进部分的部件加速比\

F_e:被改进部分原执行时间占原来总时间的百分比

$$

为使系统能获得较高加速比,可改进部分必须占有较大的比例。

当对一个系统中的某个部件进行改进后,所能获得的整个系统性能的提高,受限于该部件的执行时间占总执行时间的百分比。

CPU性能公式

在设计CPU的时候,部件加速比往往是不能得到的。

一个程序在CPU上运行的时间不包括I/O时间。

CPU时间=执行程序所需的时钟周期x时钟周期时间。

时钟周期时间:系统的时钟周期时间越短,相应的CPU性能越好(纯粹依赖硬件实现)

时钟周期数:固有属性

- 指令周期数CPI:平均每条指令耗费的时钟周期数

$$

CPI=\frac{执行程序所需的时钟周期数}{IC}\

IC:所执行的指令条数

$$

- 指令周期数CPI:平均每条指令耗费的时钟周期数

处理器性能优化的策略

$CPU时间=IC\times CPI\times 时钟周期时间$

- 减少指令条数

- 降低CPI

- 减少时钟周期时间

局部性原理

- 时间局部性:如果一个信息正在被访问,那么它很有可能即将被访问

- 空间局部性:程序即将用到的信息很有可能与目前正在使用的信息在空间上相邻或者临近。

局部性原理最能在存储部分中体现出来。例如:经常性事件放置在cache中。

提高并行性的技术

并行性:同时性+并发性

- 同时性:两个及以上事件在同一时刻发生

- 并发性:两个及以上事件在同一时间间隔内发生

从处理数据的角度,并行性等级:

- 字串位串:每次只对一个字的一位进行处理

- 字串位并:同时对一个字的全部位进行处理,不同字之间是串行的

- 字并位串:同时对许多字的同一位进行处理

- 全并行:同时对许多字的全部位或部分位进行处理

从执行程序的角度,并行性等级:

- 指令内部并行:单条指令中各微操作之间的并行

- 指令级并行:并行执行多条指令

- 线程级并行:并行执行多个线程

- 任务级或过程级并行:并行执行多个过程、任务(程序段)

- 作业、程序级并行:并行执行多个作业、程序

提高并行性的方法:

- 时间重叠:让多个处理过程轮流重叠的使用用一套硬件设备的各个部分,加快硬件周转

- 资源重复:重复设置硬件资源,大幅度地提高计算机系统的性能

- 资源共享:软件方法,使得多个任务按一定时间顺序轮流使同一套设备

单机系统下的并行性的发展

时间重叠

在高性能单处理机过程中,起主导作用的是时间重叠原理。

实现时间重叠的基础:部件功能专用化。

把一件工作按功能分割为多个部分,每个部分指定给专门的部件完成。

资源重复

主要运用在多体储存器、多操作部件和阵列处理机。

资源共享

本质是用单处理机模拟多处理机的功能,以形成虚拟机的功能。

计算机系统评价

性能

评价指标:响应时间(完成一个任务的全部时间)、吞吐率(单位时间完成的任务数)

$$

MIPS = \frac{指令条数}{执行时间X10^6}=\frac{f}{CPIX10^6}\

程序执行时间T_c = \frac{指令条数}{MIPSX10^6}\

MFLOPS = \frac{程序中的浮点操作数}{执行时间X10^6}

$$成本

售价构成能耗

可靠性

冯诺依曼结构的发展改进

输入输出方式的改进

1、程序等待:CPU需要轮询I/O设备,造成CPU时间浪费;

程序中断:CPU与I/O设备可并行工作

2、DMA直接存储器访问:减少CPU对I/O的干预

3、专用的I/O处理机:

4、采用并行性技术:

5、存储器组织结构的发展:相联存储器、通用寄存器组、高速缓冲存储器Cache

问答

1、衡量计算机系统设计是否优化的最通用的标准包括性能和价格。